- High performance bus system that supports multiple bus masters and provides high bandwidth operation

- Features required for high performance implemented by AMBA AHB:

- Burst transfers

- Split transactions

- Single cycle bus master handover

- Single clock edge operation

- Wider data bus configuration (64/128 bits)

Components of AMBA AHB

- AMBA master: A bus master is able to initiate read/write operations by providing an address and control information

- AMBA Slave: A bus slave responds to a read/write operation within a given address space range

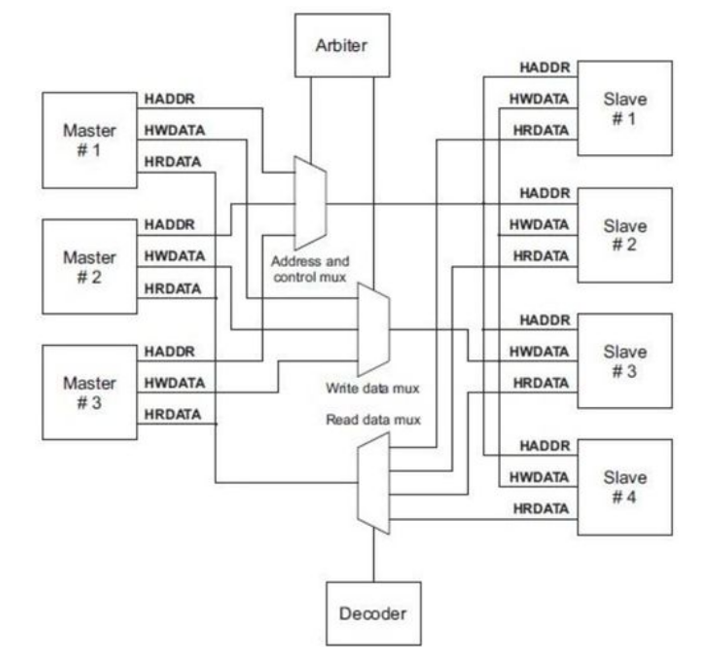

- AHB Arbiter The bus arbiter ensures that only one bus master at a time is allowed to initiate data transfers

- AHB Decoder: The AHB Decoder is used to decode the address of each transferred provide a select signal for the slave that is involved in the transfer.

Typical Master and Slave

- An AMBA AHB system may contain one or more bus masters

- A system would contain at least the processor and the test interface

- Typical for a DMA (Direct Memory Access) or DSP (Digital Signal Processor) to be included as bus masters

- The external memory interface, APB bridge and any internal memory are the most common AHB slaves

- Any other peripheral in the system could also be included as an AHB slave.

BUS cases

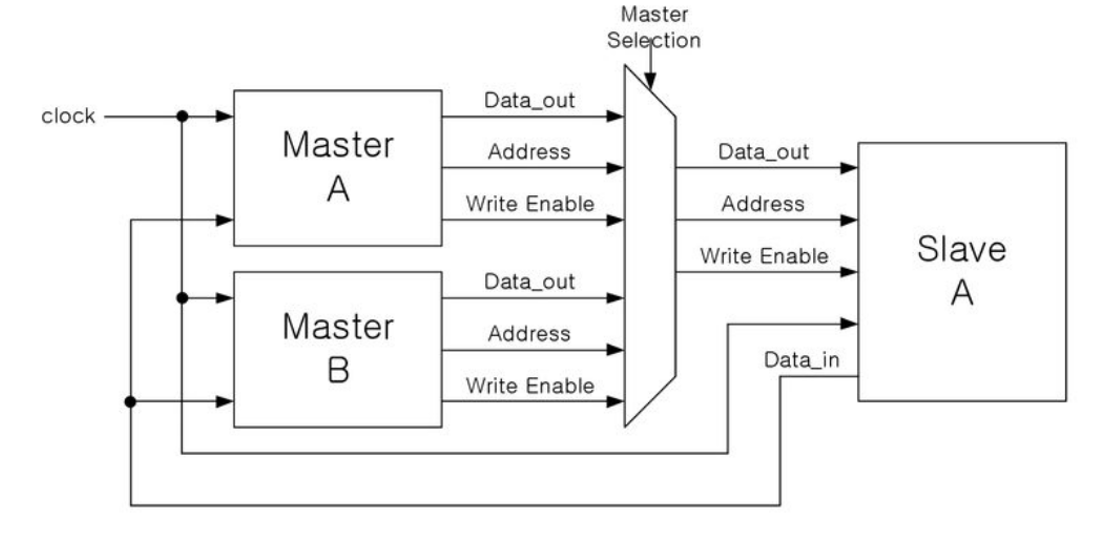

Single Master Single Slave (SMSS)

- No requirement of a bus

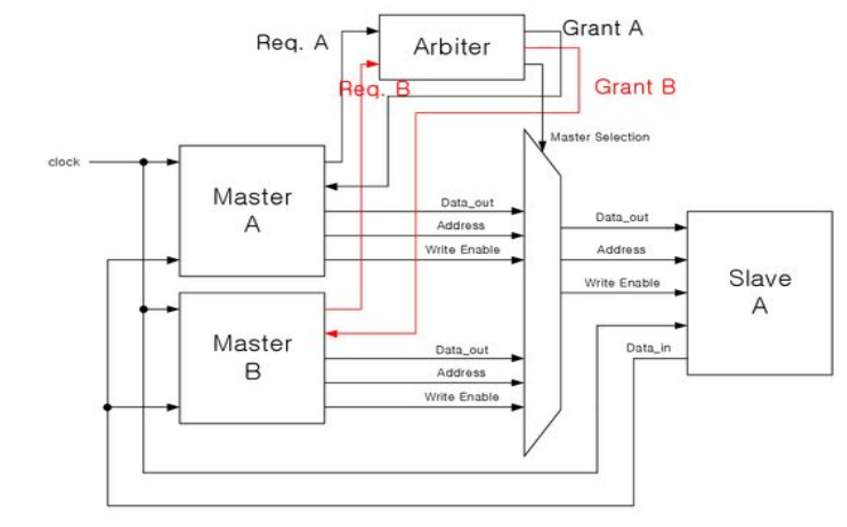

Multi Master Single Slave (MMSS)

Master selection has to be done by an external entity, an Arbiter.

Master selection has to be done by an external entity, an Arbiter.

- When a master wants to transfer data, it sends a request signal to the arbiter

- If the arbiter grants the request, then the master transfers data.

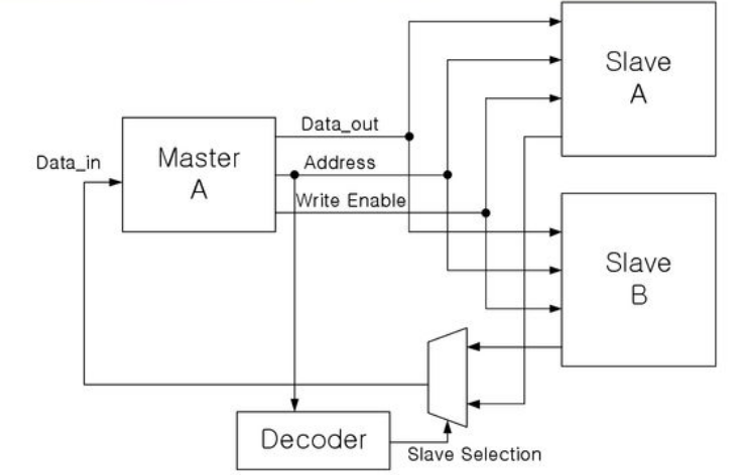

Single Master Multi Slave (SMMS)

In this case, the slave selection is done by a decoder

In this case, the slave selection is done by a decoder

- A decoder takes input from the master’s address bar and decodes which slave will transfer the data to the master.

Multi Master Multi Slave (MMMS)

AMBA Signals

| Signal | Description |

|---|---|

| HRESET | Reset |

| HADDR | Address |

| HWDATA | Data from master to slave |

| HWRITE | Write enable |

| HRDATA | Data from slave to master |

| HREADY | Indicates slave is ready |

| HREQUESTx | Request from master number x to arbiter |

| HGRANTx | Grant from arbiter to master number x |

| HSELx | Section signal from decoder to slave |

Process of an AMBA AHB operation

- Bus master must be granted access to the bus

- Process begins when master asserts a request signal to the arbiter

- Arbiter indicates when the master will be granted the use of the bus

- Arbiter grants use of the bus when ready

- A granted bus master starts an AMBA AHB transfer by driving the address and control signals

- These signals provide information on the address, direction and width of the transfer, as well as an indication if the transfer forms part of a burst

- A write data is used to move data from the master to a slave, while a read data bus is used to move data from a slave to the master.